News

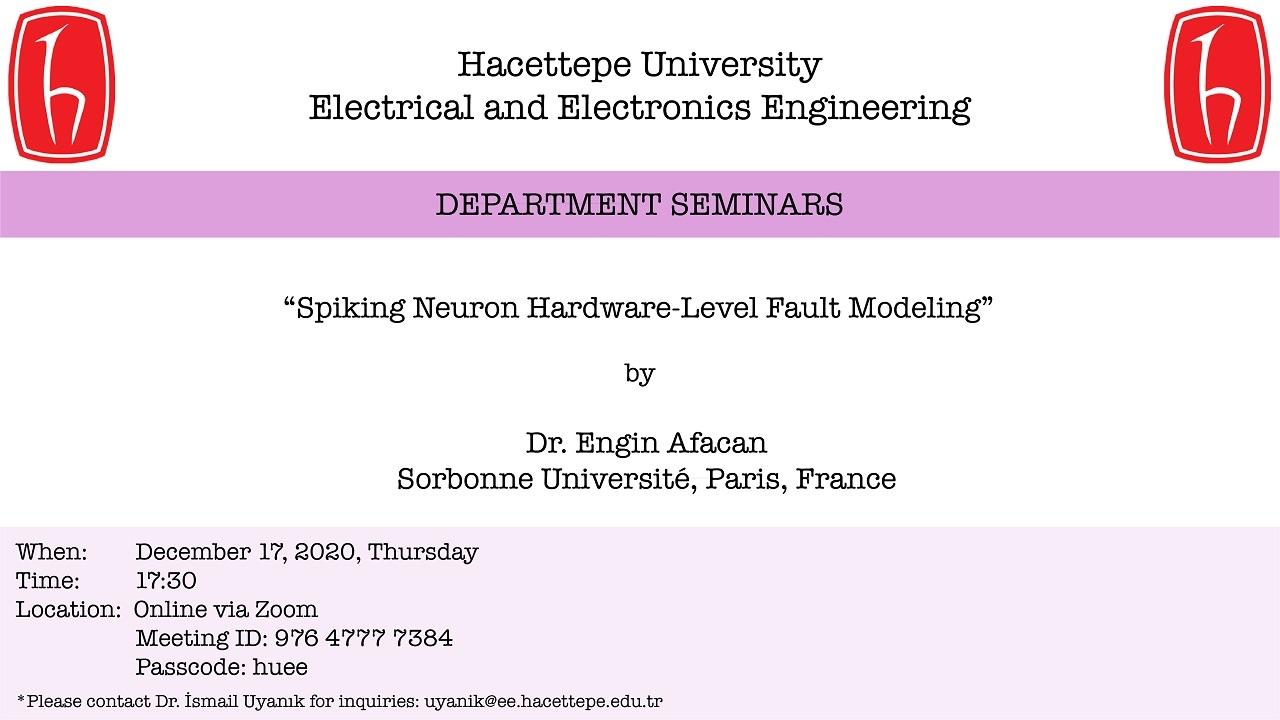

ONLINE SEMINAR: Spiking Neuron Hardware-Level Fault Modeling, Dr. Engin Afacan, Thursday, Dec. 17, 2020, 17:30, Zoom

December 14, 2020

Within the department's seminar series of 2020-2021 Fall Term, Dr. Engin Afacan will make a talk titled "All-Optical Information Processing using Diffractive Neural Networks".

For your questions and comments:

Dr. İsmail Uyanık, uyanik@ee.hacettepe.edu.tr

Seminar Date : Thursday, December 17, 2020

Seminar Time : 17:30 (Turkey local time)

Seminar Place : Zoom

Zoom id and passcode is on the image below.

For your questions and comments:

Dr. İsmail Uyanık, uyanik@ee.hacettepe.edu.tr

ABSTRACT

The deployment of Artificial Intelligence (AI) hardware accelerators in a variety of applications, including safety critical ones, requires assessing their inherent reliability to hardware-level faults and developing cost-effective fault tolerance techniques. This entails performing large- scale fault simulation experiments. However, transistor-level fault simulation is prohibitive and fault simulation should be carried out at a higher abstraction level. In this work, we focus on spiking neural networks (SNNs), and we follow a bottom-up approach starting from transistor-level simulations for developing a neuron behavioral-level fault model that can be readily employed for performing behavioral-level fault simulation of deep SNNs.

Biography

Dr. Engin Afacan received his B.Sc degree from Electronics and Communication Engineering, Kocaeli University, Turkey in 2009, the M.Sc. degree and the Ph.D. degree from Electrical and Electronics Engineering, Bogazici University, Istanbul, Turkey in 2011 and 2016, respectively. Dr. Afacan worked as research and teaching assistant at Electrical and Electronics Engineering, Boğaziçi University between 2009-2016. He is a full-time Professor (Assistant) at Electronics and Communication Engineering, Kocaeli University, Turkey. Currently, he is working as a post-doctorate researcher in Laboratoire d'Informatique Paris 6, Sorbonne Université, Paris, France. His current research interest centers on CAD/EDA tools, analog/RF circuit design and automation, aging and variability modeling, reliability- aware CMOS analog circuit design and automation, hierarchical analog circuit synthesis, Analog IP, reconfigurable analog circuit design, and hardware implementations of fault-tolerant artificial neural networks.

The deployment of Artificial Intelligence (AI) hardware accelerators in a variety of applications, including safety critical ones, requires assessing their inherent reliability to hardware-level faults and developing cost-effective fault tolerance techniques. This entails performing large- scale fault simulation experiments. However, transistor-level fault simulation is prohibitive and fault simulation should be carried out at a higher abstraction level. In this work, we focus on spiking neural networks (SNNs), and we follow a bottom-up approach starting from transistor-level simulations for developing a neuron behavioral-level fault model that can be readily employed for performing behavioral-level fault simulation of deep SNNs.

Biography

Dr. Engin Afacan received his B.Sc degree from Electronics and Communication Engineering, Kocaeli University, Turkey in 2009, the M.Sc. degree and the Ph.D. degree from Electrical and Electronics Engineering, Bogazici University, Istanbul, Turkey in 2011 and 2016, respectively. Dr. Afacan worked as research and teaching assistant at Electrical and Electronics Engineering, Boğaziçi University between 2009-2016. He is a full-time Professor (Assistant) at Electronics and Communication Engineering, Kocaeli University, Turkey. Currently, he is working as a post-doctorate researcher in Laboratoire d'Informatique Paris 6, Sorbonne Université, Paris, France. His current research interest centers on CAD/EDA tools, analog/RF circuit design and automation, aging and variability modeling, reliability- aware CMOS analog circuit design and automation, hierarchical analog circuit synthesis, Analog IP, reconfigurable analog circuit design, and hardware implementations of fault-tolerant artificial neural networks.

More news